# **M8091CKCA**

Electrical receiver conformance test application for IEEE 802.3ck

### Introduction

The M8091CKCA electrical receiver conformance test application enables accurate and repeatable receiver test procedures following the IEEE 802.3ck Draft 3.3 recommendations to ensure interoperability between datacom interfaces with a lane rate of 106 Gbps. The test procedures are based on the Channel Operating Margin (COM) method for chip-to-chip (C2C) testing and on the stressed eye method for chip-to-module (C2M) testing.

## **Key Features**

• 100GAUI-1, 200GUI-2, 400GAUI-4 C2C and C2M interfaces testing following recommendations from IEEE 802.3ck (Draft 3.3)

#### Annex 120F Chip-to-Chip (C2C)

- o 120F.3.2.4 Receiver Interference Tolerance Test

- o 120F.3.2.5 Receiver Jitter Tolerance Test

#### Annex 120G Chip-to-Module (C2M) Host & Module Input

- o 120G.3.3.5 Host Stressed Input Test

- o 120G.3.4.3 Module Stressed Input Test

- C2M test coverage includes near-end and far-end host input test and module input test with highand low-loss channel

- Guided setup, automated stressed signal calibration and pre-conformance measurement

- HTML test report

- · Remote control & data analytics

- Choose between node-locked, transportable, network, USB-dongle perpetual license

# **Description**

The M8091CKCA electrical receiver conformance test application is designed to assist and simplify the stressed signal calibration used for testing the inputs of IEEE 802.3ck Draft 3.3 chip-to-chip (C2C) and chip-to-module (C2M) electrical interfaces using either a Keysight M8040A 64Gbaud Higher Performance BERT or a Keysight M8050A 120Gbd High-Performance BERT combined with a Keysight Digital Communication Analyzer (DCA) time-equivalent oscilloscope or Infinitium UXR real-time oscilloscope. It reduces user interaction to a minimum and performs all required calibration routines and compliance testing automatically by remote-controlling all required instruments. At the same time, it offers flexibility to test different scenarios within or beyond the standard recommendations.

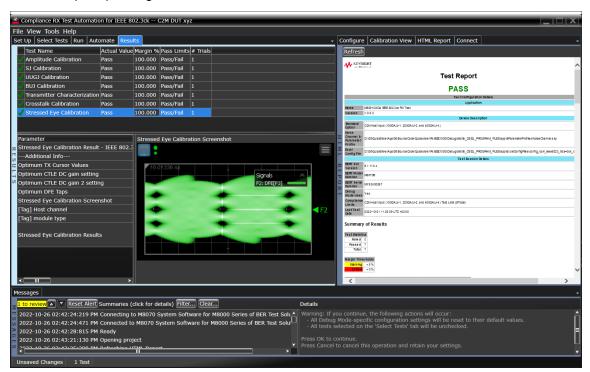

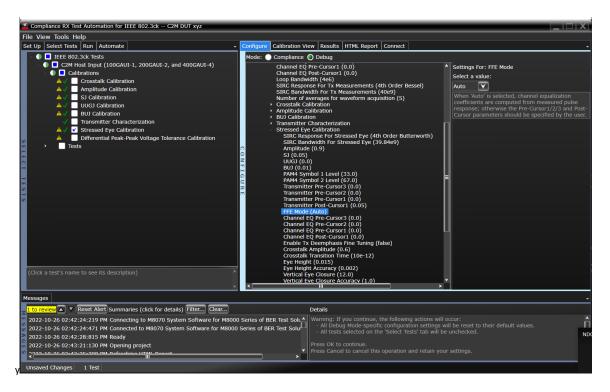

Figure 1. Graphical user interface of the M8091CKCA IEEE 802.3ck conformance receiver test application

The test application utilizes the same framework as other Keysight conformance test applications, thus reducing the training time and offering the functionalities remote control, scripting, and automated pdf or HTML-based test report generation. The user is guided by means of diagrams as well as text to minimize errors. Results of the individual calibration steps and tests are presented in tabular form as well as graphical form, where appropriate. Calibrations and test results can be stored in projects and recalled later.

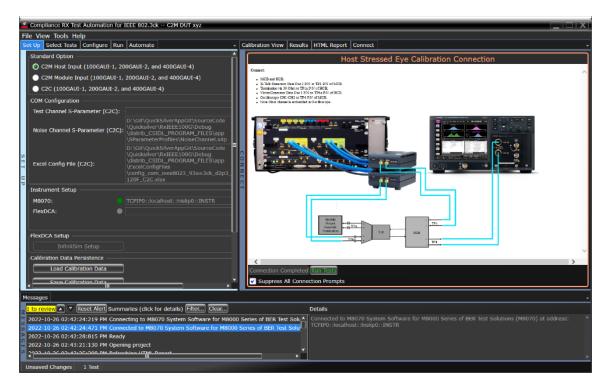

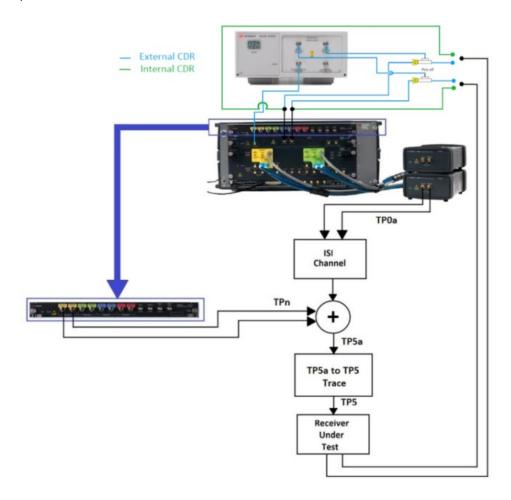

Figure 2. Connection diagram for chip-to-module, C2M host input test calibration

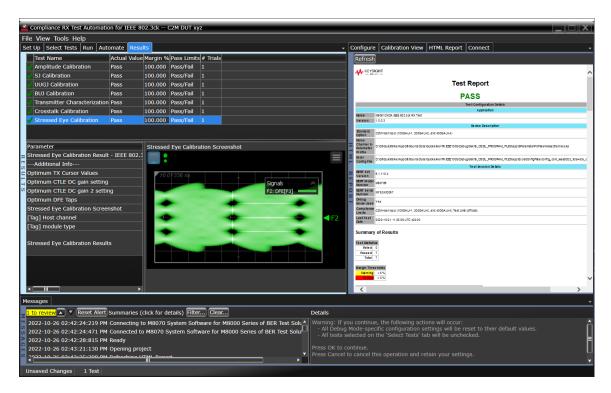

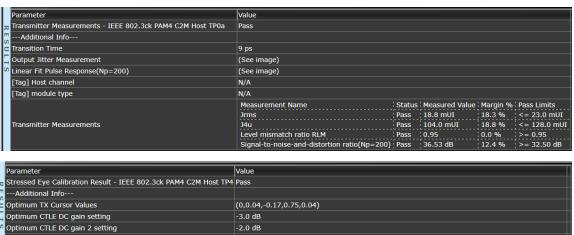

Figure 3. Results of a C2M calibration

| Parameter                                                        | Value                                                                 |         |         |          |                      |            |           |

|------------------------------------------------------------------|-----------------------------------------------------------------------|---------|---------|----------|----------------------|------------|-----------|

| Stressed Eye Calibration Result - IEEE 802.3ck PAM4 C2M Host TP4 | Stressed Eye Calibration Result - IEEE 802.3ck PAM4 C2M Host TP4 Pass |         |         |          |                      |            |           |

| Additional Info                                                  |                                                                       |         |         |          |                      |            |           |

| Optimum TX Cursor Values                                         | (0,0.04,-0.17,0.75,0.0                                                | 04)     |         |          |                      |            |           |

| Optimum CTLE DC gain setting                                     | -3.0 dB                                                               |         |         |          |                      |            |           |

| Optimum CTLE DC gain 2 setting                                   | -2.0 dB                                                               |         |         |          |                      |            |           |

| Optimum DFE Taps                                                 | (0.152426,0.025403,                                                   | 0.01176 | 7,0.014 | 52)      |                      |            |           |

| Stressed Eye Calibration Screenshot                              | (See image)                                                           |         |         |          |                      |            |           |

| [Tag] Host channel                                               | far end                                                               |         |         |          |                      |            |           |

| [Tag] module type                                                | short                                                                 |         |         |          |                      |            |           |

|                                                                  | Standard Parameter                                                    | Status  | Target  | Measured | Instrument Parameter | Nominal    | Actual    |

| Stressed Eye Calibration Results                                 | EH5                                                                   |         |         |          | Amplitude            |            | 599 mV    |

|                                                                  | VEC5                                                                  | Pass    | 12dB    | 11.6dB   | RJ                   | 0.00000 UI | 21.27 mUI |

**Figure 4.** Results of the reference transmitter characterization (top) and stressed eye calibration for chip-to-module host input (bottom)

# Calibrations and Tests Covered by M8091CKCA

## 100GAUI-1, 200GAUI-2, 400GAUI-4 C2C (chip-to-chip)

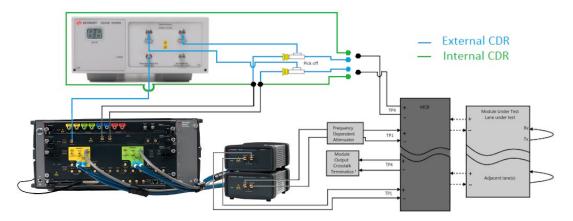

The chip-to-chip C2C test procedures defined in IEEE 802.3ck, Draft 3.3, Annex 120F rely on the Channel Operating Margin (COM) method <sup>1</sup>. COM was first introduced to measure the performance margin of a channel and then extended to digital systems. Interoperability of digital receiver can be expressed in terms of COM requirements. COM is calculated using channel 4-ports S-parameters (for victim and aggressor lanes) as well as the noise and equalization functionality of the considered transmitter and receiver. The resulting COM metric is the ratio of the signal amplitude (after equalization) to the noise and crosstalk peak-to-peak amplitude measured during a time interval depending on the target BER.

IEEE 802.3ck C2C receiver test calibration procedure consists of three steps <sup>2</sup>.

- 1. *System calibration*: Calibrate the equipment used to generate the victim transmitter and the broadband noise (once per setup configuration).

- 2. Channel characterization: S-parameter measurements using a network analyzer.

<sup>2</sup> For more details on these standards, refer to IEEE Standard for Ethernet, IEEE 802.3, Annex 120F.

<sup>1</sup> IEEE Standard for Ethernet, IEEE 802.3, Annex 93A.

- 3. COM-related calibration: The following steps are performed to complete the COM model

- a. Verify channel compliance based on S-parameter analysis.

- b. Measure transmitter characteristics (jitter & electrical characteristics), which can be adjusted to test different scenarios.

- c. Compute the amount of broadband noise required for a specific channel operating margin (usually 3dB) and inject it into the noise path to test the receiver (BER measurement for different levels of noise or jitter)

After calibration, the C2C receiver interference tolerance test and receiver jitter tolerance test can be performed.

Figure 5. Setup configuration for C2C receiver interference tolerance test

Please note that this receiver conformance test application covers only the tests for Inference Tolerance (120F.3.2.4) and Jitter Tolerance (120F.3.2.5). Other test parameters such as Difference Effective Return Loss, dERL (120F.3.2.2) and Differential to Common-mode Return Loss (120F.3.2.3) are not covered within this test application. The dERL (120F.3.2.2) can be measured with the N1091CKCA electrical TX test application for IEEE802.3ck that applies the same ERL methodology and with reference to the same procedure in 93A.5 with the values in Table 120G-2 and Table 120G-7.

## 100GAUI-1, 200GAUI-2, 400GAUI-4 C2M (chip-to-module)

The M8091CKCA implements both *host* and *module stressed input test* procedures defined in IEEE 802.3ck, Draft 3.3, Annex 120G. The procedure is based on the stressed eye method, where the metrics of the test signal such as eye height (EH) and vertical eye closure (VEC) are adjusted at the output of the mated host compliance board (HCB) or module compliance board (MCB) connection towards values defined in the standard by tuning the transmitter amplitude, de-emphasis, and jitter profile. When carried out manually, this calibration procedure is very time-consuming. The M8091CKCA receiver test application performs this task automatically.

Figure 6. Setup configuration for C2M module stressed input test

IEEE C2M receiver test calibration procedure consists of the following steps:

- 1. Crosstalk calibration <sup>3</sup>: The aggressor lane slew time and amplitude are adjusted to meet the specified target. A third-party source can be used as an aggressor channel. In this case, the calibration must be carried out manually.

- 2. System calibration: Calibrate the amplitude and jitter (sinusoidal, BUJ, UUGJ) of the pattern generator used to generate the victim transmitter (optional, recommended once per setup configuration).

- 3. *Transmitter characterization*: In this step, the transmitter characteristics (rise time, SNDR, jitter profile) are measured and compared to the requirements for compliant transmitters. Note that different transmitter profiles can be used as starting points for the stressed eye calibration (optional, recommended once per setup configuration).

- 4. Stressed signal calibration: The transmitter de-emphasis and receiver equalizer are first optimized. This step is optional but highly recommended to ensure successful calibration. Otherwise, optimal Tx-de-emphasis settings must be provided by the user. After this, the signal amplitude and random jitter are adjusted to meet the target Eye Height (EH), defined at 1e-5 probability and Vertical Eye Closure (VEC) metrics.

<sup>3</sup> The requirements of the Crosstalk Calibration for the Host and Module Stressed Inputs cannot be met with the M8045A pattern generator. Please refer to the Release Notes for more information and workaround.

## **C2M** stressed input test calibration recommendations

C2M stress mix and calibration targets (Draft 3.3)

|                                                          | Module input test                             | Host input test |  |

|----------------------------------------------------------|-----------------------------------------------|-----------------|--|

| Sinusoidal Jitter (refer to table 120G-9)                |                                               | 50 mUI          |  |

| Random Jitter (RJ) and Bounded Uncorrelated Jitter (BUJ) | inject if required to meet EH and VEC targets |                 |  |

| VEC (refer to table 120G-8 & 120G-10)                    |                                               | 12-12.5 dB      |  |

| EH refer to table 120G-8 & 120G-10)                      | 10 mV                                         | 15 mV           |  |

# Input voltage tolerance test for C2M host input and C2M module input

The host and module input voltage tolerance test procedures as defined in IEEE 802.3ck, Draft 3.3, Annex 120G validate the acceptance of the differential input peak-to-peak amplitudes produced by the extreme operating conditions from the transmitter. Please note that this receiver conformance test application covers only the Chip-to-Module (C2M) Stressed Input Test<sup>4</sup> (120G.3.3.5 for host input & 120G.3.4.3 for module input) and Peak-to-Peak Voltage Tolerance Test (120G.5.1 for both host input & module input).

Other test parameters such as the Effective Return Loss, ERL (120G.3.3.4 for host input & 120G.3.4.4 for module Input) are not covered within this test application. The ERL measurement can be measured with the N1091CKCA electrical Tx test application for IEEE 802.3ck that applies same ERL methodology and with reference to the same procedure in 93A.5 with the values in Table 120G-6 and Table 120G-9. Note that the test channel S-parameter file is required for the ERL measurement, which needs to be measured manually.

<sup>4</sup> We recommend using the automated transmitter de-emphasis optimization and a VEC accuracy of 1 dB to ensure a successful calibration.

# **Configuration Guide**

The table below shows the required equipment for each standard option under IEEE 802.3ck Annex 120F (chip-to-chip, C2C) and 120G (chip-to-module, C2M). Required instrument configuration and required software options are listed in the following section.

| Equipment type           | C2M                                                                    | C2C                                  |  |

|--------------------------|------------------------------------------------------------------------|--------------------------------------|--|

| Victim pattern generator | M8045A or M8042A                                                       |                                      |  |

| Crosstalk generator      | 2nd channel of M8045A/M804<br>or third-party crosstalk genera          | <del></del>                          |  |

| Interference source      | N.A.                                                                   | M8054A or M8196A or M8194A           |  |

| Victim error detector    | M8046A or M8043A or DCI (DUT Control Interface available in M8070ADVB) |                                      |  |

| Clock recovery           | M8046A – 0A4/ 0A5 (internal CDR)                                       |                                      |  |

| Oscilloscope             | N100                                                                   | N1000A + N1060A DCA-X or             |  |

|                          | UXR-series oscillos                                                    | scopes with 59 GHz bandwidth & above |  |

## Minimum required instrument configuration

The options marked \* are recommended but not mandatory.

#### M8000 BERT system

| M8040A-BU2 or           | Bundle consisting of one M9505A 5-slot AXIe Chassis with USB option                  |

|-------------------------|--------------------------------------------------------------------------------------|

| M8050A-BU2 or           | Bundle consisting of one M9505A 5-slot AXIe Chassis with USB option                  |

| M8050A-BU4 <sup>5</sup> | Bundle consisting of two M9505A 5-slot AXIe Chassis with USB                         |

| M8070B                  | System software for M8000 Series of BER test solutions (version 10.0.160.6 or later) |

#### Choose between M8040A or M8050A BERT platform

|        |             | M8040A                                                                                           |

|--------|-------------|--------------------------------------------------------------------------------------------------|

| M8045A |             | Pattern generator and clock module 32/64 Gbaud, 3 slot AXIe                                      |

| 0      | M8045A-G64  | Pattern Generator one Channel NRZ, Data Rate up to 64 GBaud (Requires Remote Head, e.g., M8057B) |

| 0      | M8045A-0G2* | Second Channel, Hardware and License (requires M8057B Remote Head)                               |

| 0      | M8045A-801  | Short cable, 1.85 mm (m) to 1.85 mm (m) (2 for each M8057B recommended)                          |

| 0      | M8045A-0G3  | Advanced Jitter Sources for Receiver Characterization, Module-wide License                       |

| 0      | M8045A-0G4  | De-emphasis, Module-wide License                                                                 |

| 0      | M8045A-0P3  | PAM-4 Encoding up to 34 GBaud, Module-wide License                                               |

| ٥      | M8045A-0P6  | PAM-4 Extension up to 64 GBaud, Module-wide License                                              |

| 0      | M8057B-FG   | Remote Head for M8045A Pattern Generator, 1 Channel                                              |

| 0      | M8045A-803  | Short cable, 1.85 mm (m) to 1.85 mm (m) (2 for each M8057B recommended)                          |

<sup>5</sup> A two-chassis approach is required for the M8050A-based configuration covering C2M and C2C when an external error detector is required.

9

#### M8050A

| M8042A |             | Pattern Generator Module 32/64/120 GBd, 2 or 3-slot AXIe                                    |

|--------|-------------|---------------------------------------------------------------------------------------------|

| ٥      | M8042A-0G1  | Pattern Generator NRZ and PAM4, 1 Channel, 2-slot AXIe Modu (requires M8058A Remote Head)   |

| 0      | M8042A-G64  | Pattern Generator, 64 GBd for NRZ and PAM4, module-wide License                             |

| 0      | M8042A-0G4  | De-emphasis, module-wide License                                                            |

| ٥      | M8042A-0G2* | Pattern Generator NRZ and PAM4, 2 Channel, 3-slot AXIe Module (requires M8058A Remote Head) |

| M8058A |             | Remote Head, 32/64 GBd for M8042A Pattern Generator                                         |

| 0      | M8058A-801  | Matched Cable Pair, 1.85 mm (m) to 1.85 mm (m), 2 ps, 0.15 m                                |

| M8009A |             | Clock Generator Module with Jitter Modulation, 60 GHz, 1 slot AXIe                          |

| 0      | M8009A-061  |                                                                                             |

| 0      | M8009A-0G3  | Advanced Jitter Modulation for up to two Channels, License                                  |

|        |             |                                                                                             |

#### Configure the error analyzer <sup>6</sup>

| M8046A | ١                     | Analyzer module, 32/64 Gbaud 1-slot AXIe                       |

|--------|-----------------------|----------------------------------------------------------------|

| 0      | M8046A-A64            | Analyzer, one Channel, Data Rate up to 64 GBaud, NRZ           |

| 0      | M8046A-0A4*           | Clock recovery for 32 Gbaud, License                           |

| 0      | M8046A-0A5*           | Clock recovery for Extension up to 64 Gbaud License            |

| 0      | M8046A-0P3            | PAM-4 decoding up to 32 GBaud, License                         |

| ٥      | M8046A-0P6            | PAM-4 Extension up to 58 GBaud, License                        |

| ٥      | M8046A-0A3            | Equalizer License                                              |

| ٥      | M8046A-802*           | Matched cable pairs, two matched cable pairs are required      |

| ٥      | M8046A-801            | Cable 2.92 mm (m) to 2.92 mm (m), 0.5 m for clock input, Qty 1 |

| M8043A | <b>A</b>              | Analyzer Module 32/64 Gbaud, NRZ and PAM4 2-slot AXIe          |

| 0      | M8043A-0A3            | Equalizer License                                              |

| o      | M8043A-A64            | Analyzer, one Channel, Data Rate up to 64 GBaud, NRZ and PAM4  |

| N1076B | 3/N1078A <sup>7</sup> |                                                                |

| 0      | N107xx-264            | Supported input rates 125 MBd to 64 GBd                        |

| 0      | N1076B-CR1            | Clock Recovery Phase Matching Kit for N076B Electrical         |

| ٥      | N1076B-2PB            | Microwave Pick-off Tee 1.85 mm connectors, matched pair        |

| ٥      | 11900B                | 2.4 mm female to 2.4 mm female adapter                         |

| 0      | 83059A                | Coaxial Adapter, 3.5 mm Male-Male                              |

|        |                       |                                                                |

#### Select an interference source for the C2C application

Not required if internal error counters of the device under test are used.

Choose on external N107xx Clock Recovery if M8046A-A04/-A05 options not selected. Not required when DUT internal error counter is used.

| M8194A |            | 120 GSa/s Arbitrary Waveform Generator            |

|--------|------------|---------------------------------------------------|

| 0      | M8194A-001 | Arbitrary Waveform Generator, 1 Channel 120 GSa/s |

| M8196A |            | 92 GSa/s Arbitrary Waveform Generator             |

| 0      | M8196A-001 | Arbitrary Waveform Generator 1 Channel 92 GSa/s   |

| M8054A |            | Interference Source 32 GHz                        |

#### DCA-X mainframe and precision waveform analyzer configuration

| N1000A |            | DCA-X Wide-Bandwidth Oscilloscope Mainframe           |

|--------|------------|-------------------------------------------------------|

| •      | N1000A-PLK | Pattern Lock Trigger Hardware Model                   |

| N1060A |            | Precision Waveform Analyzer                           |

| •      | N1060A-050 | Two 50 GHz channels                                   |

| •      | N1060A-EVA | Equalizer Integrated variable                         |

| •      | N1060A-264 | Supported input rates 125 MBd to 64 GBd               |

| 0      | N1060A-PTB | Precision Timebase Ultra/Low Random Jitter            |

| 0      | N1060A-JSA | Jitter Spectrum Analysis and Clock Recovery Emulation |

#### UXR

| • UXR059A/B | 59GHz, Infiniium UXR-Series real-time Oscilloscope                                                |

|-------------|---------------------------------------------------------------------------------------------------|

| D9020ASIA   | Advanced signal integrity software (EQ, InfiiniSimAdv, crosstalk)                                 |

| D9010PAMA   | Pulse amplitude modulation PAM-N analysis software                                                |

| D9020JITA   | Jitter, vertical and phase noise analysis software for 90000, V-, Z- and UXR-series oscilloscopes |

#### Accessories & fixtures (recommended)

| M8195A-810              | Cable, 2.92 mm (m) to 2.92 mm (m), length-0.85 m (for combining SI and RI)                                   |

|-------------------------|--------------------------------------------------------------------------------------------------------------|

| M8195A-820              | Coaxial termination 50 Ω DC to 26.5 GHz, 3.5 mm (male) (2 required)                                          |

| SP0602A                 | Wilder OSFP 112G/800G MCB 1.85 mm Receptacle Test Adapter                                                    |

| SP0603A                 | Wilder OSFP 112G/800G HCB Plug 1.85 mm Test Adapter                                                          |

| SP0606A                 | Wilder QSFP-DD 112G/800G MCB 1.85 mm Receptacle Test Adapter                                                 |

| SP0607A                 | Wilder QSFP-DD 112G/800G HCB Plug 1.85 mm Test Adapter                                                       |

| M8045A-802 <sup>8</sup> | Matched directional coupler pair, 50 GHz, 13 dB, 2.4 mm                                                      |

| -                       | Wilder DCOM-ISI-112G-9CH-36F-1.85, Datacom ISI 112G 9-Channel Board for (C2M and C2C low-loss and high-loss) |

| M8067A-001              | ISI Channel Board Three Traces 6.2, 11.7, and 17.1 inches, 1.85 mm Connectors (for C2M and C2C high-loss)    |

#### Software configuration

| M8070ADVB-1xx | Advanced Measurement Package for M8000 Series of BERT Test Solutions (node locked, transportable, floating or USB license, revisions 9.1 or later) |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| M8091CKCA-1xx | Pre-compliance RX Test Automation for IEEE 802.3ck (node-locked, transportable floating or USB license)                                            |

| N1010100A     | Research and Development Package for FlexDCA-DCA-X mainframe minimum configuration <sup>9</sup>                                                    |

#### Additional ordering information

| S1201A CSI Bundle | S1201A IEEE 802.3ck Tx and Rx Conformance Test |

|-------------------|------------------------------------------------|

|                   | Solution                                       |

## **Minimum PC configuration**

The PC running the application should meet the following requirements

PC Hardware requirements

- Operating system: Microsoft Windows 10 (64 bit), Version 1809 or newer

- Memory: 8 GB RAM minimum

- Monitor resolution: WXGA+ (1440 x 900) minimum

PC Software requirements

- · Microsoft Office 2019 or higher

- Microsoft .NET Framework 4.7.1 or newer

- · Keysight IO Library Suite Rev. 18.1

- Keysight License Manager 5 and Keysight License Manager 6

- Keysight M8070B system software for M8000 series

- o Ver.10.0.160.6

- o M8070ADVB Advanced Measurement Package for M8000 Series Ver. 1.6.180.2

- o M8194A soft front panel version 2.0.31.0 or later or M8196A soft front panel version 2.1.1.0

- Keysight DCA-X oscilloscope FW rev. A.07.41.27

- Keysight UXR oscilloscope FW rev. 11.50.00601

- MATLAB compiler runtime R2017a (9.2)

<sup>9</sup> Corresponding legacy DCA options: N1010AT-200/-201/-0EP/-SIM

12

## **Remote Programming**

The M8091CKCA Conformance Receiver Test Application for IEEE 802.3ck is part of Keysight's Digital Test Apps and can be programmed via ARSL, any .NET language. For more information, see <a href="https://www.keysight.com/find/rpi">www.keysight.com/find/rpi</a>.

# **Data Analytics Enabled**

This test application supports data exporting with support from the Keysight KS6800A Data Analytics Software. For more information see <a href="https://www.keysight.com/find/data-analytics">www.keysight.com/find/data-analytics</a>.

## **Related products**

The N1091CKCA Electrical TX Test Software for IEEE 802.3ck (100/200/400 Gb/s) for sampling oscilloscopes offers automated transmitted testing for IEEE PAM-4 based electrical outputs.

The D90103CKC Electrical TX Test Software for IEEE 802.3ck (100/200/400 Gb/s) for real-time oscilloscopes offers automated transmitter testing for IEEE PAM4-based electrical outputs.

The N4917BSCB Optical Receiver Stress Test Application addresses test needs for optical input test of transceiver modules for IEEE 400GBASE-based optical interfaces.

The N19301B PLTS Base Analysis is the industry standard for signal integrity measurements and data post-processing of high-speed interconnects, such as cables, backplanes, PCBs and connectors.